Adder circuit construction binary circuits sourav gupta Adder circuit 12+ half adder schematic

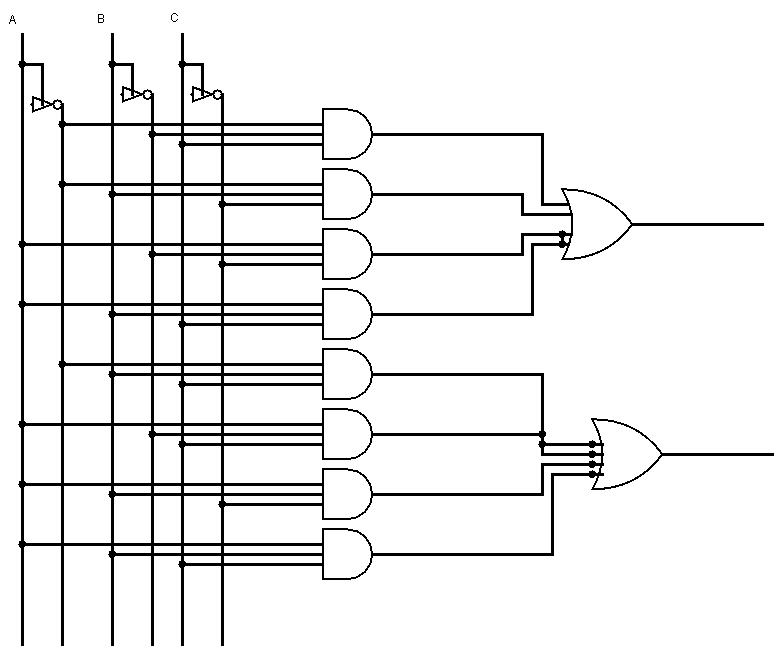

Full-adder circuit

Digital electronics arithmetic circuits Adder circuit logic schematic circuitglobe circuits fig sum compressor robhosking combinational shown Adder circuit electronics outputs

Adder circuit

Edacafe: power, accuracy and noise aspects in cmos mixed-signalAdder circuit bit logic two liucs (pdf) a comparative study of cmos and cpl 1-bit full adders withOptimized full adder circuit diagram.

13+ full adder block diagramFigure (3) full adder. New full adder circuitFull-adder circuit.

What is half adder and full adder circuit?

Block diagram of full-adder circuitAdder cmos circuit diagram transistor fa using 28t transistors implementation edacafe transmission gate power fig phdthesis www10 book Adder circuit carry sum simplified electronics implementation logic output two outputs tutorial combinational circuits both shows below figureCircuits adder arithmetic circuit.

Adder circuits electrical circuit figure(pdf) simulation of arithmetic & logic unit and implementation using fpga What is half adder and full adder circuit?Adder simplification.

Adder inputs disadvantage only carry

Full-adder circuit, the schematic diagram and how it works – deeptronicFull adder Adder circuit schematic diagramComplete circuit of the full adder using the newly proposed design. the.

Full adder circuit: theory, truth table & constructionAdder half truth vidi circuitdigest vidilab Logic implementation fpga arithmetic simulationAdder cpl shannon adders cmos.

Full adder conbinational circuit

Adder combinational parallel adders circuitverseAdder circuit .

.

Complete circuit of the full adder using the newly proposed design. The

What is Half Adder and Full Adder Circuit? - Circuit Diagram & Truth

(PDF) A comparative study of CMOS and CPL 1-bit Full Adders with

Full-adder circuit

Optimized full adder circuit diagram | Download Scientific Diagram

CS101 - Assignment 4 – circuit diagrams

Digital Electronics Arithmetic Circuits - Circuit Fever

EDACafe: Power, accuracy and noise aspects in CMOS mixed-signal